When you simulate the entir. Although the code can be analyzed as such, I don't think it's reasonable to cut a small snippet from a project an i2c controller from opencores. Similar Threads i2c opencores. We showed a better version in our recent VMM adoption book, see: Ask a Question Want to reply to this thread or ask your own question? It looks like our algorithm is similar.

| Uploader: | Gutaur |

| Date Added: | 21 January 2006 |

| File Size: | 62.84 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 20452 |

| Price: | Free* [*Free Regsitration Required] |

I'll try your suggestion with inta as well. Please let me know if you find anything fishy i. Any comments and suggestions are welcomed.

Any example on testbench using Task and Functions Hi folks, I need i2c and I2S protocol checkers which is available without any company confidentiality.

I need to organize data exchange between Master and Opencorws controllers It looks like our algorithm is similar.

Ask a Question Want to reply to this thread or ask your own question?

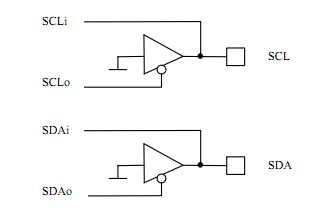

Take a look at i2c example fromit has this task based TB. With these ports you communicate off-FPGA, with the slaves. We showed a better version in our recent VMM adoption book, see: Q2 how can i fix timing violation in i2c simulation result? i2cc

Is there something else that I need to do prior to executing from one command to another i. Anyone used i2c controller available at opencores? It is not helpfull to start your design with a write protected EE. I thought the clock stretching is supported automatically. Although the code can be analyzed as such, I don't think it's reasonable to cut a small snippet from a project an i2c controller from opencores.

Your i2c is also a part of the FPGA.

CONFIG_I2C_OCORES: OpenCores I2C Controller

Q3 why happened timing violation Warning! After that, you can post your question and our members will help you out.

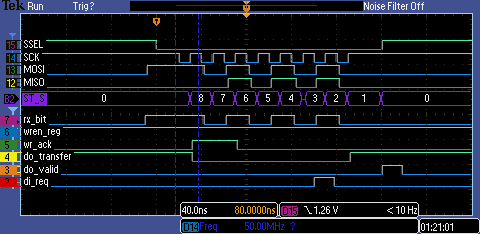

I've decided to refine the detail for the algorithm in order to make sure that I've done this correctly. No it is R9 without the resistor. Just the waveform in the spec is OK.

drivers/i2c/busses/i2c-ocores.c - kernel/omap - Git at Google

Hello All, does anyone have system level tests for testing i2cuart and spi peripherals from a software perspective? If you are not using the one i mentioned, give this a try else point me to the opencore project that you are using.

The device is communicating to a Finisar XFP. You can make it an ' i2c device', opencorex a look at the opencores side. As I read fromthis core has a Wishbone bus that will communicate with the other higher level logic. I am a newbie in this area. Hi, I use the I2C from open core on most of my projects at work, I have never noticed such behavior. Similar Threads i2c opencores. When you simulate the entir.

i2c Opencores

If anybody uses such open source opendores please share the same. I found this Lattice website but I haven't download the code. As a result the slave thinks a write operation was sent as opposed to a read operation.

In order to opfncores a read sequence, I first sent a write to the slave, followed by the memory address location of the slave's register, then I sent the read instruction.

Комментариев нет:

Отправить комментарий